Tutorial NOR Gate SR Latch Circuit

by Lewis Loflin

Back to Hobby Electronics What to Know

Here we will learn the operation of a NOR gate SR latch. From that we will construct a D flip-flop.

Related see the YouTube video NOR Gate SR Latch

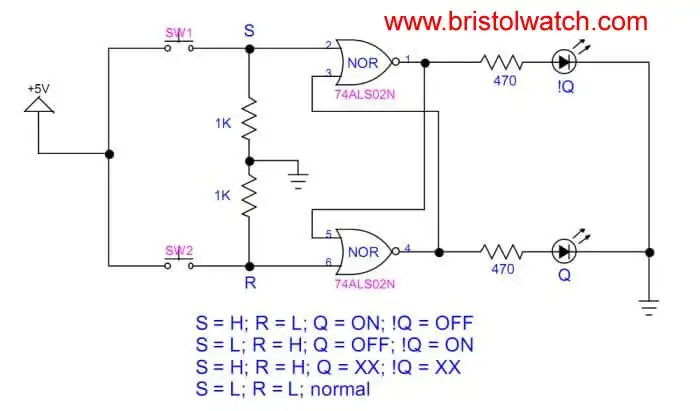

A SR latch is a form of a bistable multivibrator. It has two stable states, as indicated by the prefix bi in its name. Typically, one state is referred to as set and the other as reset. The simplest bistable device, therefore, is known as a set-reset, or S-R, latch. To create an S-R latch, we can wire two NOR (or NAND) gates in such a way that the output of one feeds back to the input of another, and vice versa.

Here I will address the NOR gate version.

The Q and not-Q outputs are supposed to be in opposite states. But both forms of SR latches have illegal input states. For a NOR gate latch both input HIGH turns off both output LEDs.

Having both S and R equal to 1 is called an invalid or illegal state for the S-R multivibrator. Otherwise, making S=1 and R=0 "sets" the multivibrator so that Q=1 and not-Q=0. Conversely, making R=1 and S=0 "resets" the multivibrator in the opposite state. When S and R are both equal to 0, the multivibrator's outputs "latch" in their prior states.

This is opposite for a NAND gate based SR Latch. Both input LOW turns both LEDs ON. See Basic NAND Gate SR Latch Circuit.

Ref. Wiki

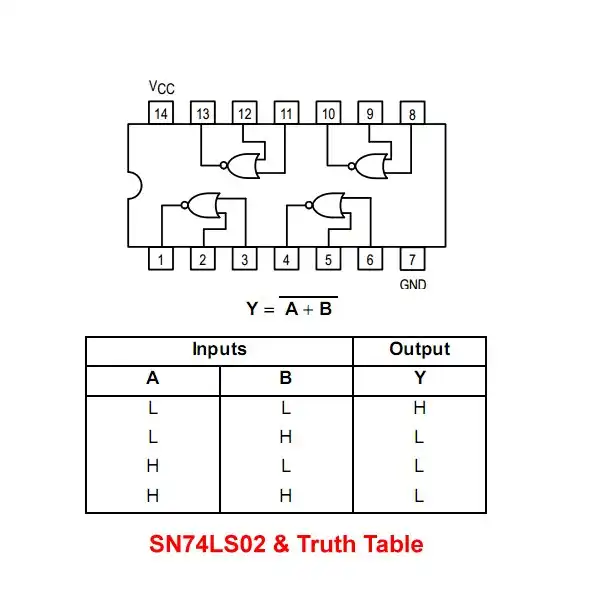

Compare the above truth table for a 74LS02 to the 74LS00 Quad 2-Input NAND Gates. Both gate types have two inputs, but the outputs differ.

Normally the inputs are left LOW for the NOR gate latch, but are normal HIGH in the NAND gate version. This created differing input electrical connections.

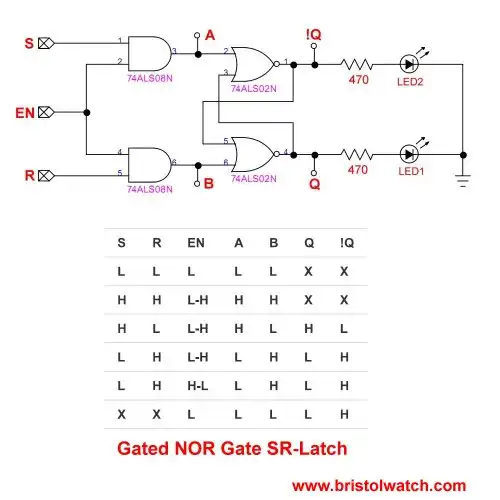

Above is a gated version of a NOR gate SR latch. We use two 74LS08 AND gates on the inputs. Only when EN goes LOW to HIGH to LOW do we change Q and !Q.

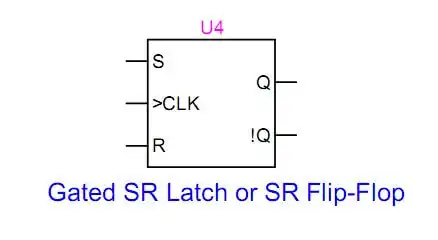

At this point we have a gated SR Latch. Note the new symbol.

Note in the table two LOW inputs are still illegal even if gated. We will solve this with a D flip-flop.

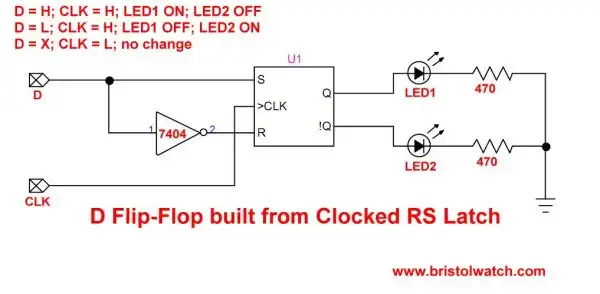

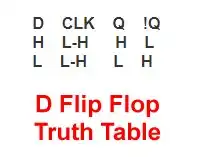

Above we added an inverter between S and R. This prevents S and R from both being HIGH or LOW. The new single input is DIN. This forms a D flip-flop. Note the following table:

Note the change happens when CLK goes LOW to HIGH then LOW.

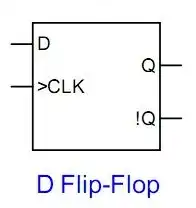

Finally if built from NAND or NOR gates the final D flip-flop is identical.

- Digital Circuits:

- Simple Schmitt Trigger SN74HC14 Square Wave Generator

- Introduction to RC Differentiator Circuits and Uses

- SN74HC14 Square Wave Generator uses SN7476 JK Flip-Flop

- Three Output Pulse Generator Circuit for Digital Circuits

- Astable CD4047 Geiger Counter Power Supply

- CD4047 Monostable Multivibrator Circuit

- Basic TTL Tri-State Buffer Circuit Examples

- Tutorial NOR Gate SR Latch Circuits

- Tutorial NAND Gate SR Latch Circuit

- Tutorial OR-NOR Circuits Including Monostable Multivibrator

- Brief Tutorial of XOR and XNOR Logic Gates

- LM555-NE555 One-Shot Multivibrator AC Power Control

- YouTube:

- Three Output Digital Pulse Generator

- Opto-Coupler SCR and Triac Circuits:

- Improved AC Zero Crossing Detectors for Arduino

- Zero-Crossing Detectors Circuits and Applications

- Simple Triac-SCR Test Lab

- Light Activated SCR Based Optocouplers Circuit Examples

- Comparing Photo Triac, Photo SCR Opto-Couplers

- Silicon Controlled Rectifier Review and Circuits

- Silicon Controlled Rectifiers Connected as Power Triacs

- Using Zero-Crossing Detectors with Arduino

- Hardware Interrupts Demo and Tutorial for Arduino

- In Depth Look at AC Power Control with Arduino

- Micro-controller AC Power Control Using Interrupts

- Light Activated SCR Based Optocouplers Circuit Examples

- Solid State AC Relays with Triacs

- YouTube

- Zero-Crossing Detectors Circuits and Applications

- Zero-Crossing Circuits for AC Power Control

- In Depth Look at AC Power Control with Arduino

- Micro-controller AC Power Control Using Interrupts

- YouTube Video for Arduino AC Power Control

- Arduino

- Arduino PWM to Analog Conversion

- Arduino Analog Digital Conversion Voltmeter

- Better Arduino Rotary Encoder Sensor

- Simple 3-Wire MAX6675 Thermocouple ADC Arduino Interface

- YouTube:

- 3-Wire MAX6675 Thermocouple ADC Arduino Interface

- Exploring Solid State Relays and Control Circuits

- Comparing Photo Triac, Photo SCR Opto-Couplers

- Light Activated SCR Based Optocouplers Circuit Examples

- Silicon Controlled Rectifier Review and Circuits

- Silicon Controlled Rectifiers Connected as Power Triacs

- Insulated Gate Bipolar Transistor IGBT Circuits

- Current Limiter Circuits for Opto-Coupler LEDs

- VOM1271 Photovoltaic MOSFET Driver Circuits

- Current Limiter Allows Safe Testing of Zener Diodes, LEDs

- 3 Amp LM741 Op-Amp Constant Current Source

- Bidirectional Solid State Relay Circuits

- Simple Solid State Relay for Low Power LED 120V Lamps

- Build High Power MOSFET Directional Switch Relay

- Optical Isolation of H-Bridge Motor Controls

- All NPN Transistor H-Bridge Motor Control

- Basic Transistor Driver Circuits for Micro-Controllers

- ULN2003A Darlington Transistor Array with Circuit Examples

- Tutorial Using TIP120 and TIP125 Power Darlington Transistors

- Driving 2N3055-MJ2955 Power Transistors with Darlington Transistors

- Understanding Bipolar Transistor Switches

- N-Channel Power MOSFET Switching Tutorial

- P-Channel Power MOSFET Switch Tutorial

- Build a Transistor H-Bridge Motor Control

- H-Bridge Motor Control with Power MOSFETS

- More Power MOSFET H-Bridge Circuit Examples

- Build a High Power Transistor H-Bridge Motor Control

- H-Bridge Motor Control with Power MOSFETS Updated

- Opto-Isolated Transistor Drivers for Micro-Controllers

- Comparator Theory Circuits Tutorial

- Constant Current Circuits with the LM334

- LM334 CCS Circuits with Thermistors, Photocells

- LM317 Constant Current Source Circuits

- TA8050P H-Bridge Motor Control

- All NPN Transistor H-Bridge Motor Control

- Basic Triacs and SCRs

- Comparator Hysteresis and Schmitt Triggers

- Comparator Theory Circuits Tutorial

- Photodiode Circuits Operation and Uses

- Optocoupler MOSFET DC Relays Using Photovoltaic drivers

- Connecting Crydom MOSFET Solid State Relays

- Photodiode Op-Amp Circuits Tutorial

- Optocoupler Input Circuits for PLC

- H11L1, 6N137A, FED8183, TLP2662 Digital Output Optocouplers

- Optical Isolation of H-Bridge Motor Controls

- All NPN Transistor H-Bridge Motor Control

© Copyright 2019 Lewis Loflin E-Mail